# DATA SHEET

# MOS INTEGRATED CIRCUIT

$\mu$ PD17240,17241,17242,17243,17244,17245,17246

# 4-BIT SINGLE-CHIP MICROCONTROLLERS FOR SMALL GENERAL-PURPOSE INFRARED REMOTE CONTROL TRANSMITTERS

#### **DESCRIPTION**

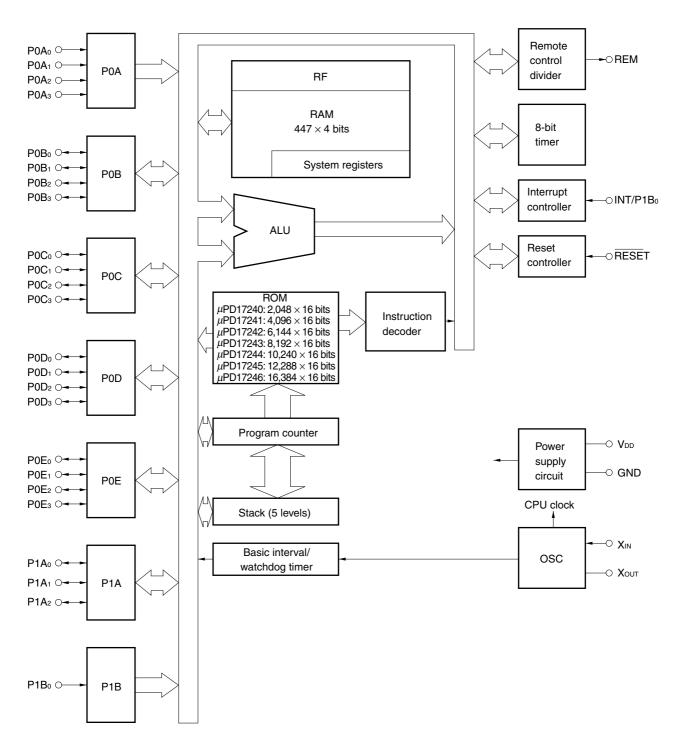

The  $\mu$ PD17240, 17241, 17242, 17243, 17244, 17245, 17246 (hereafter called the  $\mu$ PD17246 Subseries) are 4-bit single-chip microcontrollers for small general-purpose infrared remote control transmitters.

This subseries employs 17K general-purpose register system architecture for the CPU, and can directly execute operations between data memories instead of the conventional method of executing operations through an accumulator. Moreover, all the instructions are 16-bit/1-word instructions, enabling efficient programming.

In addition, a one-time PROM model, the  $\mu$ PD17P246, to which data can be written only once, is also available. This product is convenient either for evaluating the  $\mu$ PD17246 Subseries programs or for small-scale production of application systems.

Detailed function descriptions are provided in the following user's manual. Be sure to read them before designing.

μPD172×× Subseries User's Manual: U12795E

#### **FEATURES**

- Infrared remote controller carrier generator (REM output)

- 17K architecture: General-purpose register system

- Program memory (ROM), data memory (RAM)

|                         | μPD17240             | μPD17241             | μPD17242              | μPD17243              | μPD17244               | μPD17245               | μPD17246               |

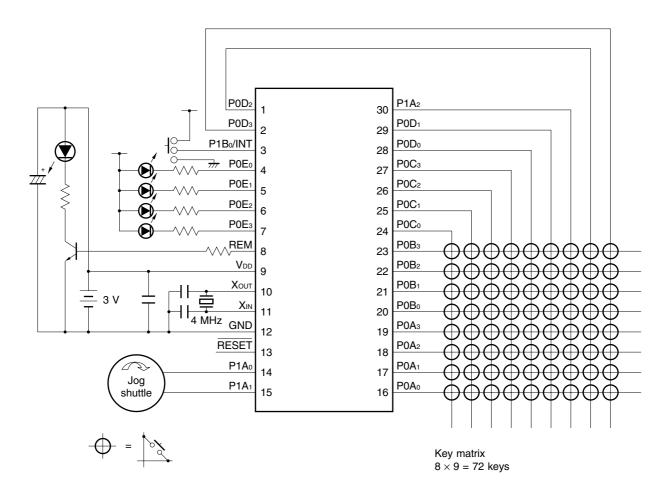

|-------------------------|----------------------|----------------------|-----------------------|-----------------------|------------------------|------------------------|------------------------|

| Program<br>memory (ROM) | 4 KB<br>(2,048 × 16) | 8 KB<br>(4,096 × 16) | 12 KB<br>(6,144 × 16) | 16 KB<br>(8,192 × 16) | 20 KB<br>(10,240 × 16) | 24 KB<br>(12,288 × 16) | 32 KB<br>(16,384 × 16) |

| Data memory<br>(RAM)    | 447 × 4 bits         |                      |                       |                       |                        |                        |                        |

8-bit timer: 1 channelBasic interval timer/watchdog timer: 1 channel

Instruction execution time (can be changed in two steps)

@ fx = 4 MHz: 4  $\mu$ s (high-speed mode)/8  $\mu$ s (normal mode)

External interrupt pin (INT/P1B<sub>0</sub>): 1I/O pins: 24

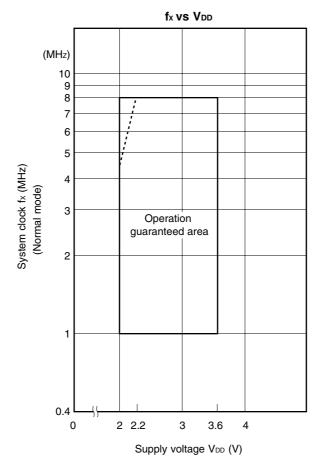

• Supply voltage:  $V_{DD} = 2.0 \text{ to } 3.6 \text{ V}$

On-chip RAM retention detectorLow-voltage detector (mask option)

Unless otherwise specified, the  $\mu$ PD17246 is treated as the representative model throughout this document.

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all products and/or types are available in every country. Please check with an NEC Electronics sales representative for availability and additional information.

# **APPLICATIONS**

Preset remote controllers, toys, portable systems, etc.

# **ORDERING INFORMATION**

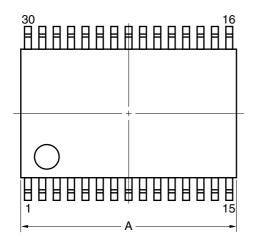

| Part Number                             | Package                             |

|-----------------------------------------|-------------------------------------|

| μPD17240MC-××-5A4                       | 30-pin plastic SSOP (7.62 mm (300)) |

| $\mu$ PD17241MC-××-5A4                  | 30-pin plastic SSOP (7.62 mm (300)) |

| $\mu$ PD17242MC-××-5A4                  | 30-pin plastic SSOP (7.62 mm (300)) |

| $\mu$ PD17243MC- $\times$ $\times$ -5A4 | 30-pin plastic SSOP (7.62 mm (300)) |

| $\mu$ PD17244MC- $\times$ $\times$ -5A4 | 30-pin plastic SSOP (7.62 mm (300)) |

| $\mu$ PD17245MC- $\times$ $\times$ -5A4 | 30-pin plastic SSOP (7.62 mm (300)) |

| $\mu$ PD17246MC- $\times$ $\times$ -5A4 | 30-pin plastic SSOP (7.62 mm (300)) |

Remark ××× indicates ROM code suffix.

# NEC

# DIFFERENCES BETWEEN $\mu \text{PD17246}$ SUBSERIES, $\mu \text{PD17236}$ SUBSERIES, AND $\mu \text{PD17255}$ SUBSERIES (1/2)

| Item                                                                                             | μPD17246 Subseries                                                                                                                                                                                                                                      | μPD17236 Subseries                                                                                                                                                                                                                                         | μPD17225 Subseries                                                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROM                                                                                              | $\mu$ PD17240: 2,048 × 16 bits $\mu$ PD17241: 4,096 × 16 bits $\mu$ PD17242: 6,144 × 16 bits $\mu$ PD17243: 8,192 × 16 bits $\mu$ PD17244: 10,240 × 16 bits $\mu$ PD17245: 12,288 × 16 bits $\mu$ PD17246: 16,384 × 16 bits $\mu$ PD17246: 447 × 4 bits | $\mu$ PD17230: 2,048 × 16 bits $\mu$ PD17231: 4,096 × 16 bits $\mu$ PD17232: 6,144 × 16 bits $\mu$ PD17233: 8,192 × 16 bits $\mu$ PD17234: 10,240 × 16 bits $\mu$ PD17235: 12,288 × 16 bits $\mu$ PD17236: 16,384 × 16 bits $\mu$ PD17236: 4,384 × 16 bits | μPD17225: 2,048 × 16 bits<br>μPD17226: 4,096 × 16 bits<br>μPD17227: 6,144 × 16 bits<br>μPD17228: 8,192 × 16 bits<br>μPD17228: 8,192 × 16 bits<br>111 × 4 bits<br>(μPD17225, 17226)<br>223 × 4 bits<br>(μPD17227, 17228) |

| Ports                                                                                            | P0Bo to P0B3: I/O (bit I/O) P0Co to P0C3: I/O (group I/O) P0Do to P0D3: I/O (group I/O) P1Ao to P1A2: I/O (bit I/O) P1Bo: I/O, functions alternately as INT pin                                                                                         | POBo to POBa: I/O (bit I/O) POCo to POCa: I/O (group I/O) PODo to PODa: I/O (group I/O) P1Ao: Input or output selectable by mask option                                                                                                                    | P0Bo to P0B3: Input<br>P0Co to P0C3: Output<br>P0Do to P0D3: Output                                                                                                                                                     |

| Reset  • Reset by watchdog timer  • Reset by stack pointer  • Low-voltage detector (mask option) | The RESET pin is internally pulled down by the occurrence of the internal reset signals on the left, causing a reset (usually, the RESET pin is pulled up).                                                                                             |                                                                                                                                                                                                                                                            | A low level is output from the WDOUT pin by the occurrence of the internal reset signals on the left, and a reset takes place if the WDOUT pin is externally connected to the RESET pin.                                |

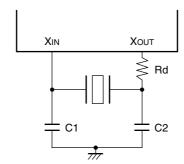

| Capacitor for oscillation                                                                        | Selected by mask option (15 pF)                                                                                                                                                                                                                         | Not provided                                                                                                                                                                                                                                               | ·                                                                                                                                                                                                                       |

| Vector address                                                                                   | Basic interval timer: 0002H Rising and falling edges of INT pin: 0003H 8-bit timer: 0004H                                                                                                                                                               | Rising and falling edges of INT pin: 0002H 8-bit timer: 0003H                                                                                                                                                                                              |                                                                                                                                                                                                                         |

| RAM retention flag                                                                               | Provided                                                                                                                                                                                                                                                | Not provided                                                                                                                                                                                                                                               |                                                                                                                                                                                                                         |

# DIFFERENCES BETWEEN $\mu \rm{PD17246}$ SUBSERIES, $\mu \rm{PD17236}$ SUBSERIES, AND $\mu \rm{PD17255}$ SUBSERIES (2/2)

| Item                                                                           | μPD17246 Subseries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | μPD17236 Subseries                                                                                                                                                                         | μPD17225 Subseries                                      |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| STOP mode release condition                                                    | <1> When any of pins P0Ao to P0A₃ goes low <2> When pins P0Bo to P0B₃, P0Co to P0C₃, and P0Do to P0D₃ are used as input pins and when any of them goes low <3> When an interrupt request (IRQ) of the interrupt for which the IP flag is set is generated at the rising edge or falling edge of the INT pin <4> When P0Eo to P0E₃ are used as input pins when a key matrix is used and when any of these pins goes low <5> When P1Ao to P1A₂ and P1Bo are used as input pins when a key matrix is used and when the level of any of these pins equals the set clear level | input pins and when any of them goes low  <3> When an interrupt request (IRQ) of the interrupt for which the IP flag is set is generated at the rising edge or falling edge of the INT pin | When any of pins P0Ao to P0A3 and P0Bo to P0B3 goes low |

| Carrier frequency (fx = 4 MHz)  NRZ low-level period setting modulo register   | Selected by register file (after reset: fx/2) <1> If carrier generation clock is fx/2: 3.9 kHz to 1 MHz <2> If carrier generation clock is fx: 7.8 kHz to 2 MHz <3> If carrier generation clock is 2fx: 15.6 kHz to 4 MHz  • NRZLTMM: 8 bits (REM output control bit is bit                                                                                                                                                                                                                                                                                               | 1 MHz<br><2> If carrier generation<br>clock is fx: 15.6 kHz to                                                                                                                             | ' '                                                     |

| (NRZLTMM) and NRZ<br>high-level period setting<br>modulo register<br>(NRZHTMM) | 1 of register file at address 12H) • NRZHTMM: 8 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | - IVINZIT I IVIIVI. / DIES (DIE / IS IIX                                                                                                                                                   | eu 10 0)                                                |

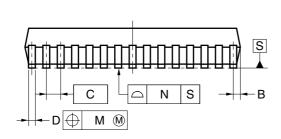

# PIN CONFIGURATION (TOP VIEW)

30-pin plastic SSOP (7.62 mm (300))

μPD17240MC-xxx-5A4, 17241MC-xxx-5A4, 17242MC-xxx-5A4, 17243MC-xxx-5A4, μPD17244MC-xxx-5A4, 17245MC-xxx-5A4, 17246MC-xxx-5A4

GND: Ground

INT: External interrupt request signal input

$P0A_0$  to  $P0A_3$ : Input port (CMOS input with pull-up resistor)

P0B $_0$  to P0B $_3$ : I/O port (CMOS input with pull-up resistor/N-ch open-drain output) P0C $_0$  to P0C $_3$ : I/O port (CMOS input with pull-up resistor/N-ch open-drain output) P0D $_0$  to P0D $_3$ : I/O port (CMOS input with pull-up resistor/N-ch open-drain output)

$P0E_0$  to  $P0E_3$ : I/O port (when key matrix is used: CMOS input with pull-up resistor/N-ch open-

drain output, when key matrix is not used: CMOS input/push-pull output)

P1A<sub>0</sub>/P1A<sub>2</sub>: Input port (when key matrix is used: CMOS input/N-ch open-drain output, when

key matrix is not used: CMOS input/push-pull output)

P1B<sub>0</sub>: Input port (CMOS input)

REM: Remote controller output (CMOS push-pull output)

RESET: Reset input

VDD: Power supply

XIN, XOUT: Resonator connection

# **BLOCK DIAGRAM**

# **CONTENTS**

| 1. | PIN F | FUNCTIONS                                                                 | 9  |

|----|-------|---------------------------------------------------------------------------|----|

|    | 1.1   | Pin Function List                                                         | 9  |

|    | 1.2   | I/O Circuits                                                              | 12 |

|    | 1.3   | Handling of Unused Pins                                                   | 14 |

| 2. | MEM   | ORY SPACE                                                                 | 15 |

|    | 2.1   | Program Counter (PC)                                                      | 15 |

|    | 2.2   | Program Memory (ROM)                                                      | 18 |

|    | 2.3   | Stack                                                                     | 20 |

|    | 2.4   | Data Memory (RAM)                                                         | 22 |

|    | 2.5   | Register File (RF)                                                        | 31 |

| 3. | POR   | тs                                                                        | 34 |

|    | 3.1   | Port 0A (P0A <sub>0</sub> to P0A <sub>3</sub> )                           | 34 |

|    | 3.2   | Port 0B (P0B <sub>0</sub> to P0B <sub>3</sub> )                           | 34 |

|    | 3.3   | Port 0C (P0C <sub>0</sub> to P0C <sub>3</sub> )                           | 34 |

|    | 3.4   | Port 0D (P0D <sub>0</sub> to P0D <sub>3</sub> )                           | 34 |

|    | 3.5   | Port 0E (P0E <sub>0</sub> to P0E <sub>3</sub> )                           | 35 |

|    | 3.6   | Port 1A (P1A <sub>0</sub> to P1A <sub>2</sub> )                           | 35 |

|    | 3.7   | Port 1B (P1B <sub>0</sub> )                                               | 36 |

|    | 3.8   | INT Pin                                                                   | 37 |

|    | 3.9   | Switching Bit I/O (Port 0B, 0E, 1A)                                       | 38 |

|    | 3.10  | Selecting I/O Mode of Group I/O (Port 0C, 0D)                             | 40 |

|    | 3.11  | Selecting Whether Key Matrix Is Used or Not (Port 0E, 1A)                 | 41 |

|    |       | Specifying Resistor Connection (Port 0E, 1A)                              | 42 |

|    |       | Selecting Standby Mode Release Condition and Whether Pull-Up or Pull-Down |    |

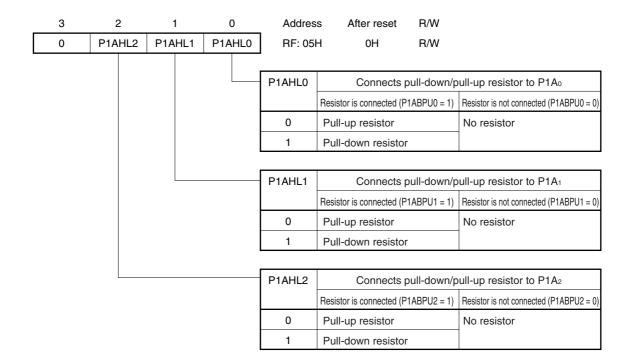

|    |       | Resistor Is Connected (Port 1A)                                           | 44 |

|    | 3.14  | Selecting Whether Key Matrix Is Used, Standby Mode Release Condition, and |    |

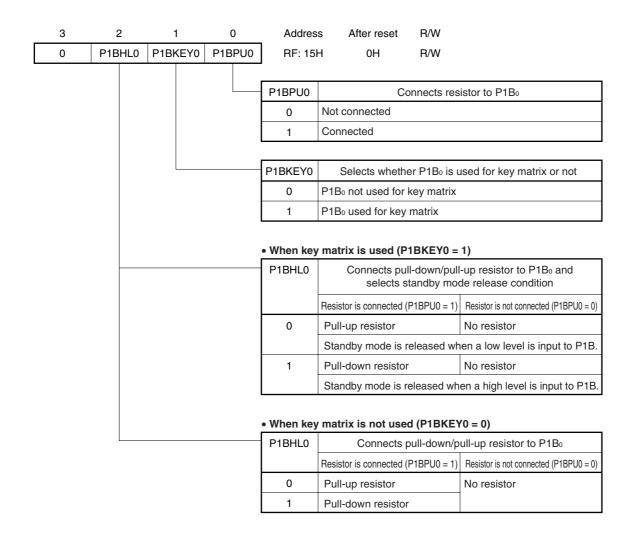

|    |       | Whether Pull-Up or Pull-Down Resistor Is Connected (Port 1B)              | 46 |

| 4. | CLO   | CK GENERATOR                                                              | 47 |

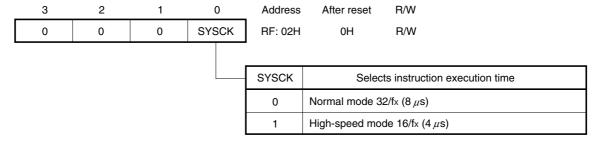

|    | 4.1   | Instruction Execution Time (CPU Clock) Selection                          | 47 |

| 5. | 8-BI1 | TIMER AND REMOTE CONTROLLER CARRIER GENERATOR                             | 48 |

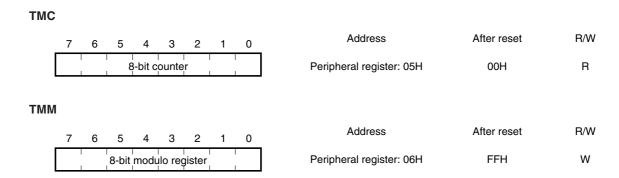

|    | 5.1   | Configuration of 8-Bit Timer (with Modulo Function)                       | 48 |

|    | 5.2   | Function of 8-Bit Timer (with Modulo Function)                            | 50 |

|    | 5.3   | Carrier Generator for Remote Controller                                   | 51 |

| 6. | BAS   | IC INTERVAL TIMER/WATCHDOG TIMER                                          | 57 |

|    | 6.1   | Source Clock for Basic Interval Timer                                     | 57 |

|    | 6.2   | Controlling Basic Interval Timer                                          | 57 |

|    | 6.3   | Operation Timing for Watchdog Timer                                       | 59 |

| 7. | RAM   | RETENTION DETECTOR                                                        | 60 |

|    | 7.1   | RAM Retention Flag                                                        | 60 |

| 8.  | INTERRUPT FUNCTIONS                                                  | 62 |

|-----|----------------------------------------------------------------------|----|

|     | 8.1 Interrupt Sources                                                | 62 |

|     | 8.2 Hardware of Interrupt Controller                                 | 63 |

|     | 8.3 Interrupt Sequence                                               | 66 |

| 9.  | STANDBY FUNCTIONS                                                    | 68 |

|     | 9.1 HALT Mode                                                        | 68 |

|     | 9.2 HALT Instruction Execution Conditions                            | 69 |

|     | 9.3 STOP Mode                                                        | 70 |

|     | 9.4 STOP Instruction Execution Conditions                            | 71 |

|     | 9.5 Releasing Standby Mode                                           | 72 |

| 10. | RESET                                                                | 73 |

|     | 10.1 Reset by Reset Signal Input                                     | 73 |

|     | 10.2 Reset by Watchdog Timer (with RESET Pin Internally Pulled Down) | 73 |

|     | 10.3 Reset by Stack Pointer (with RESET Pin Internally Pulled Down)  | 74 |

| 11. | LOW-VOLTAGE DETECTOR (WITH RESET PIN INTERNALLY PULLED DOWN)         | 75 |

| 12. | ASSEMBLER RESERVED WORDS                                             | 76 |

|     | 12.1 Mask Option Directives                                          | 76 |

|     | 12.2 Reserved Symbols                                                | 77 |

| 13. | INSTRUCTION SET                                                      | 83 |

|     | 13.1 Instruction Set Outline                                         | 83 |

|     | 13.2 Legend                                                          | 84 |

|     | 13.3 List of Instructions                                            | 85 |

|     | 13.4 Assembler (RA17K) Embedded Macro Instructions                   | 87 |

| 14. | ELECTRICAL SPECIFICATIONS                                            | 88 |

| 15. | APPLICATION CIRCUIT EXAMPLE                                          | 94 |

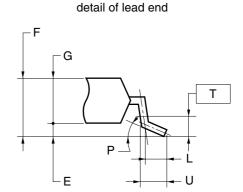

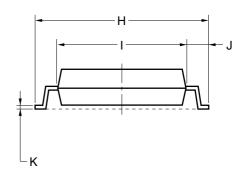

| 16. | PACKAGE DRAWING                                                      | 95 |

| 17. | RECOMMENDED SOLDERING CONDITIONS                                     | 96 |

| API | PENDIX A DIFFERENCES BETWEEN $\mu$ PD17246 AND $\mu$ PD17P246        | 97 |

| ΛDI | PENDIX B. DEVELOPMENT TOOLS                                          | 98 |

# 1. PIN FUNCTIONS

# 1.1 Pin Function List (1/3)

| Pin No.            | Pin Name                                                                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Output Format      | After Reset                                                                                |

|--------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------|

| 28<br>29<br>1<br>2 | P0D <sub>0</sub><br>P0D <sub>1</sub><br>P0D <sub>2</sub><br>P0D <sub>3</sub> | These pins constitute a 4-bit I/O port which can be set to the input or output mode in 4-bit units (group I/O).  In the input mode, these pins serve as CMOS input pins with a pull-up resistor, and can be used to input the key return signals of a key matrix. The standby status must be released when at least one of the input lines goes low. In the output mode, these pins are used as N-ch open-drain output pins and can be used to output the signals of a key matrix.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | N-ch<br>open drain | Low-level<br>output                                                                        |

| 3                  | P1B <sub>0</sub> /INT                                                        | This is an input port pin. Whether this pin functions as the P1Bo pin or the INT pin can be selected by the register file.  • P1Bo This is a 1-bit CMOS input port. This port can be used to input key return signals when a key matrix is used. At this time, whether a pull-up/down resistor is connected to this port and the standby mode release condition (whether it is released when this pin is high or low) can be selected.  1. If connection of a resistor is specified and if it is specified that the standby mode is released when this pin goes low A pull-up resistor is connected. If a low level is input to the P1Bo pin, the standby mode is released.  2. If connection of a resistor is specified and if it is specified that the standby mode is released when this pin goes high A pull-down resistor is connected. If a high level is input to the P1Bo pin, the standby mode is released.  3. If connection of a resistor is not specified and if it is specified that the standby mode is released when this pin goes low (or high) No resistor is connected. If a low (or high) level is input to the P1Bo pin, the standby mode is released.  If a key matrix is not used, whether a resistor is connected and whether the resistor is pull-up or pull-down can be selected.  • INT This is an external interrupt request signal. It can also be used to release the standby mode if an external interrupt request signal is input to this pin while the INT pin interrupt enable flag (IP) is set. |                    | P1B <sub>0</sub> input<br>(when key<br>matrix not<br>used and no<br>resistor<br>connected) |

# 1.1 Pin Function List (2/3)

| Pin No. | Pin Name         | Function                                                                                        | Output Format | After Reset   |

|---------|------------------|-------------------------------------------------------------------------------------------------|---------------|---------------|

| 4       | P0E <sub>0</sub> | These pins constitute a 4-bit I/O port that can be set to the input or                          | When key      | CMOS input    |

| 5       | P0E <sub>1</sub> | output mode in 1-bit units.                                                                     | matrix is     | (when key     |

| 6       | P0E <sub>2</sub> | If this port is set to the input mode when a key matrix is used, it                             | used: N-ch    | matrix is not |

| 7       | P0E₃             | functions as a CMOS input port with a pull-up resistor and can be                               | open-drain,   | used and no   |

|         |                  | used to input key return signals. If one of the pins of this port                               | when key      | resistor      |

|         |                  | goes low, the standby mode is released.                                                         | matrix is not | connected)    |

|         |                  | If this port is set to the output mode when a key matrix is used, it                            | used: CMOS    |               |

|         |                  | functions as an N-ch open-drain output port and can be used to output key matrix signals.       | push-pull     |               |

|         |                  | If this port is set to the input mode when a key matrix is not used,                            |               |               |

|         |                  | it functions as a CMOS input port to/from which a resistor can be                               |               |               |

|         |                  | connected/disconnected in 1-bit units. If this port is set in the                               |               |               |

|         |                  | output mode when a key matrix is not used, it functions as a high-<br>current CMOS output port. |               |               |

| 8       | REM              | Outputs transfer signal for infrared remote controller.                                         | CMOS          | Low-level     |

|         |                  | Active-high output.                                                                             | push-pull     | output        |

| 9       | V <sub>DD</sub>  | Power supply                                                                                    | _             | -             |

| 10      | Хоит             | Connects ceramic resonator for system clock oscillation.                                        | _             | (Oscillation  |

| 11      | XIN              | A capacitor (15 pF) for oscillation can be connected by using a                                 |               | stops)        |

|         |                  | mask option.                                                                                    |               |               |

| 12      | GND              | Ground                                                                                          | -             | -             |

| 13      | RESET            | System reset input. Turns ON pull down resistor if the POC or                                   | _             | Input         |

|         |                  | watchdog timer overflows and if the stack pointer overflows or                                  |               |               |

|         |                  | underflows, and resets the system. Usually, the pull-down resistor is ON.                       |               |               |

# 1.1 Pin Function List (3/3)

| Pin No.              | Pin Name                                                                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Output Format                                                        | After Reset                              |

|----------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------|

| 14<br>15<br>30       | P1A <sub>0</sub><br>P1A <sub>1</sub><br>P1A <sub>2</sub>                     | These pins constitute a 3-bit I/O port that can be set to the input or output mode in 1-bit units.  If this port is set to the input mode when a key matrix is used, it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | When key<br>matrix is<br>used: N-ch                                  | CMOS input<br>(when key<br>matrix is not |

|                      |                                                                              | functions as a CMOS input port and can be used to input key return signals. At this time, whether a pull-up/down resistor is connected to this port and the standby mode release condition (whether it is released when this pin is high or low) can be selected in 1-bit units  1. If connection of a resistor is specified and if it is specified that the standby mode is released when this port goes low  A pull-up resistor is connected. If a low level is input to the set key, the standby mode is released.  2. If connection of a resistor is specified and if it is specified that the standby mode is released when this port goes high  A pull-down resistor is connected. If a high level is input to the set key, the standby mode is released.  3. If connection of a resistor is not specified and if it is specified that the standby mode is released when this port goes low (or high)  No resistor is connected. If a low (or high) level is input to the set key, the standby mode is released.  If this port is set to the output mode when a key matrix is used, it functions as an N-ch open-drain output port and can be used to output key matrix signals.  If this port is set to the input mode when a key matrix is used, it functions as a CMOS input port.  Connection of a resistor to this port and whether the resistor is pull-up or pull-down can be selected in 1-bit units.  If this port is set in the output mode when a key matrix is not used, it functions as a high-current CMOS output port. | open-drain,<br>when key<br>matrix is not<br>used: CMOS<br>push-pull. | used and<br>no resistor<br>connected)    |

| 16<br>17<br>18<br>19 | P0A <sub>0</sub><br>P0A <sub>1</sub><br>P0A <sub>2</sub><br>P0A <sub>3</sub> | These pins are CMOS input pins with a 4-bit pull-up resistor.  They can be used to input the key return signals of a key matrix.  If any one of these pins goes low, the standby status is released.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                                    | CMOS input<br>with pull-up<br>resistor   |

| 20<br>21<br>22<br>23 | P0B <sub>0</sub><br>P0B <sub>1</sub><br>P0B <sub>2</sub><br>P0B <sub>3</sub> | These pins constitute a 4-bit I/O port that can be set to the input or output mode in 1-bit units.  In the input mode, these pins are CMOS input pins with a pull-up resistor, and can be used to input the key return signals of a key matrix. The standby status is released when at least one of these pins goes low.  In the output mode, they serve as N-ch open-drain output pins and can be used to output the key return signals of a key matrix.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | N-ch<br>open drain                                                   | CMOS input<br>with pull-up<br>resistor   |

| 24<br>25<br>26<br>27 | P0C <sub>0</sub><br>P0C <sub>1</sub><br>P0C <sub>2</sub><br>P0C <sub>3</sub> | These pins constitute a 4-bit I/O port that can be set to the input or output mode in 4-bit units (group I/O).  In the input mode, these pins are CMOS input pins with a pull-up resistor, and can be used to input the key return signals of a key matrix. The standby status is released when at least one of these pins goes low.  In the output mode, they serve as N-ch open-drain output pins and can be used to output the key return signals of a key matrix.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | N-ch<br>open drain                                                   | Low-level<br>output                      |

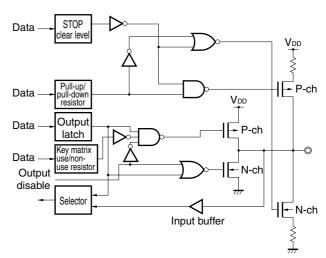

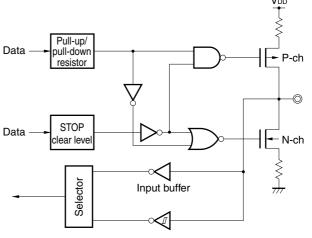

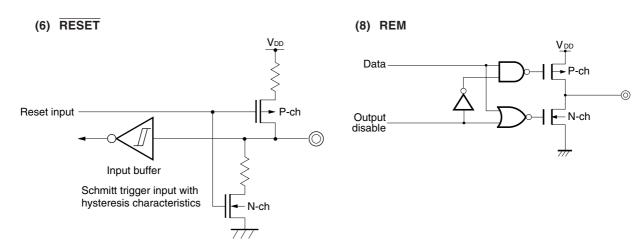

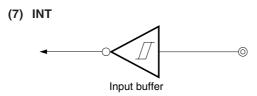

#### 1.2 I/O Circuits

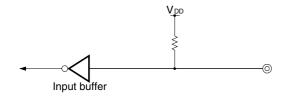

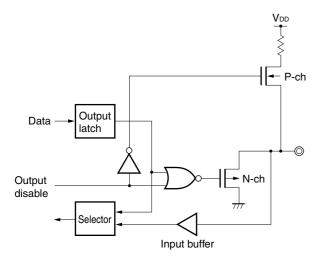

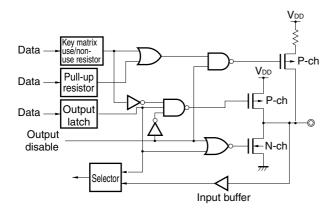

The equivalent I/O circuit for each  $\mu$ PD17246 pin is shown below.

# Figure 1-1. I/O Circuits (1/2)

(1) P0A

(2) P0B, P0C, P0D

(3) P0E

# (4) P1A

# (5) P1B

Figure 1-1. I/O Circuits (2/2)

Schmitt trigger input with hysteresis characteristics

# 1.3 Handling of Unused Pins

Handle the unused pins as follows.

Table 1-1. Handling of Unused Pins

| Pin Name                             | Recommended Connection       |  |

|--------------------------------------|------------------------------|--|

| P0A <sub>0</sub> to P0A <sub>3</sub> | Leave open.                  |  |

| P0B₀ to P0B₃                         |                              |  |

| P0C <sub>0</sub> to P0C <sub>3</sub> |                              |  |

| P0D <sub>0</sub> to P0D <sub>3</sub> |                              |  |

| P0E₀ to P0E₃                         | Connect to GND (When input). |  |

| P1A <sub>0</sub> to P1A <sub>2</sub> |                              |  |

| P1B <sub>0</sub> /INT                | Connect to GND.              |  |

| REM                                  | Leave open.                  |  |

\*

#### 2. MEMORY SPACE

#### 2.1 Program Counter (PC)

The program counter (PC) specifies an address of the program memory (ROM).

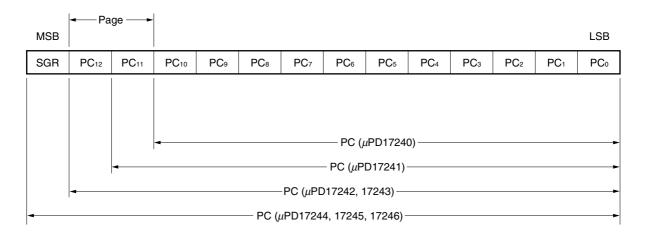

The program counter consists of an 11/12/13-bit binary counter and a 1-bit segment register (SGR) as shown in Figure 2-1.

Its contents are initialized to address 0000H at reset.

Figure 2-1. Configuration of Program Counter

#### 2.1.1 Segment register (SGR)

The segment register specifies a segment of the program memory.

Table 2-1 shows the relationship between the segment register and program memory.

Table 2-1. Relationship Between Segment Register and Program Memory

| Value of Segment Register | Segment of Program Memory |

|---------------------------|---------------------------|

| 0                         | Segment 0                 |

| 1                         | Segment 1                 |

The segment register is set when the following instructions are executed.

- BR @AR

- CALL @AR

- SYSCAL entry

The first address of the subroutine that can be called by the system call instruction ("SYSCAL entry") is the first 16 steps of each block (blocks 0 to 7) in page 0 of segment 1 (system segment).

Segment 1 (system segment) Segment 0 Block 0 of segment 1 00000H 0 2 0 0 0 H 02000H Entry address of Block 0 SYSCAL instruction 020FFH 0200FH 02100H Block 1 021FFH 0 2 2 0 0 H Block 2 Page 0 022FFH Area in which (16 bits × 2K steps) entry address of system segment can be specified 02700H Block 7 007FFH 027FFH 00800H 02800H Page 1 Page 1 00FFFH 02FFFH 01000H 03000HPage 2 Page 2 0 1 7 F F H 0 1 8 0 0 H 0 3 7 F F H 0 3 8 0 0 H Page 3 Page 3 01FFFH 03FFFH (16 bits × 8K steps) (16 bits × 8K steps)

Figure 2-2. Outline of System Call Instruction

Contents of Program Counter (PC)<sup>Note</sup> **Program Counter** Instruction SGR b<sub>12</sub> **b**10 **b**5 b<sub>11</sub> bз  $b_2$ b<sub>1</sub> bo BR addr Page 0 0 0 Page 1 0 1 tained Page 2 1 0 Operand of instruction (addr) Page 3 1 1 CALL addr Re-0 0 Operand of instruction (addr) tained SYSCAL entry 1 0 0 entryн 0 0 0 0 entry∟ BR @AR CALL @AR Contents of address register MOVT DBF, @AR RET RETSK Contents (return address) of address stack register (ASR) specified by stack pointer (SP) RETI Other instructions Re-Increment tained (including skip instruction) On acknowledging interrupt 0 Vector address of each interrupt Watchdog timer reset, RESET pin, 0 0 0 0 0 0 0 0 0 0 0 reset by stack pointer

Figure 2-3. Value of Program Counter on Execution of Each Instruction

Note  $\mu$ PD17240: b<sub>0</sub> to b<sub>10</sub>  $\mu$ PD17241: b<sub>0</sub> to b<sub>11</sub>  $\mu$ PD17242, 17243: b<sub>0</sub> to b<sub>12</sub>  $\mu$ PD17244, 17245, 17246: b<sub>0</sub> to b<sub>12</sub>, SGR

Remark entryh: Higher 3 bits of entry entryL: Lower 4 bits of entry

**Table 2-2. Interrupt Vector Address**

| Priority | Internal/External | Interrupt Source                    | Vector Address |

|----------|-------------------|-------------------------------------|----------------|

| 1        | Internal          | 8-bit timer                         | 0004H          |

| 2        | External          | Rising and falling edges of INT pin | 0003H          |

| 3        | Internal          | Basic interval timer                | 0002H          |

# 2.2 Program Memory (ROM)

The configuration of the program memory is as follows.

| Part Number | Program Memory Capacity | Program Memory Address |

|-------------|-------------------------|------------------------|

| μPD17240    | 2,048 × 16 bits         | 0000H to 07FFH         |

| μPD17241    | 4,096 × 16 bits         | 0000H to 0FFFH         |

| μPD17242    | 6,144 × 16 bits         | 0000H to 17FFH         |

| μPD17243    | 8,192 × 16 bits         | 0000H to 1FFFH         |

| μPD17244    | 10,240 × 16 bits        | 0000H to 27FFH         |

| μPD17245    | 12,288 × 16 bits        | 0000H to 2FFFH         |

| μPD17246    | 16,384 × 16 bits        | 0000H to 3FFFH         |

The program memory stores the program, interrupt vector table, and fixed data table.

The program memory is addressed by the program counter.

Figure 2-4 shows the program memory map. The entire range of the program memory can be addressed by the BD addr, BR @AR, CALL @AR, MOVT DBF, and @AR instructions. Note, however, that the subroutine entry addresses that can be specified by the CALL addr instruction are from 0000H to 07FFH.

Address  $0\,0\,0\,0\,H$ Reset start address 0001H Normal address 0002H Basic interval timer interrupt vector Page 0 Subroutine entry Branch addresses for address for CALL BR@AR instruction 0003H INT pin rising/falling edge interrupt vector addr instruction Subroutine entry 0004H 8-bit timer interrupt vector addresses for CALL@AR instruction Segment 0 Branch  $(\mu PD17240)$ 07FFH Table reference addresses for BR addr Page 1 addresses for MOVT DBF, instruction @AR instruction  $(\mu PD17241)$ 0 F F F H Page 2  $(\mu PD17242)$ 17FFH Page 3  $(\mu PD17243)$ 1FFFH 2000H Subroutine entry Page 0 address for CALL addr instruction  $(\mu PD17244)$ 27FFH Page 1 Segment 1 Branch  $(\mu PD17245)$ 2 F F F H (system addresses for BR addr segment) Page 2 instruction Page 3  $(\mu PD17246)$ 3 F F F H 16 bits

Figure 2-4. Program Memory Map

#### 2.3 Stack

A stack is a register used to save a program return address and the contents of system registers (to be described later) when a subroutine is called or when an interrupt is acknowledged.

# 2.3.1 Stack configuration

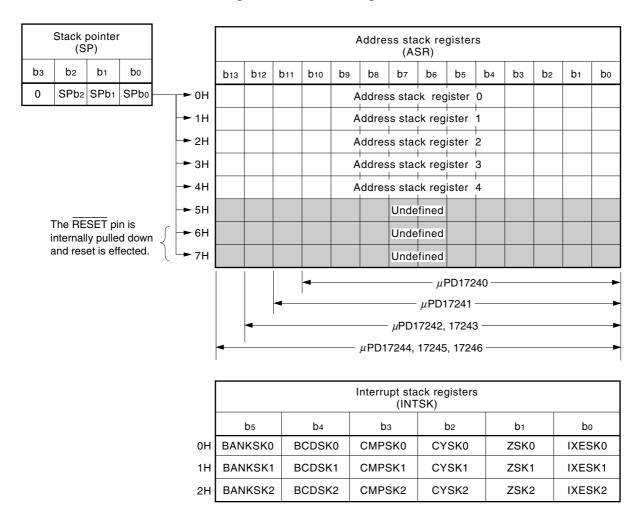

Figure 2-5 shows the stack configuration.

A stack consists of a stack pointer (a 4-bit binary counter, the highest bit fixed to 0), five 11-bit ( $\mu$ PD17240)/12-bit ( $\mu$ PD17241)/13-bit ( $\mu$ PD17242, 17243)/14-bit ( $\mu$ PD17244, 17245, 17246) address stack registers, and three 6-bit interrupt stack registers.

Figure 2-5. Stack Configuration

#### 2.3.2 Function of stack

The address stack register stores a return address when the subroutine call instruction or table reference instruction (first instruction cycle) is executed or when an interrupt is acknowledged. It also stores the contents of the address registers (ARs) when a stack manipulation instruction (PUSH AR) is executed.

If subroutines or interrupts are nested to more than 5 levels, the RESET pin is internally pulled down and a reset is effected.

The interrupt stack register (INTSK) saves the contents of the bank register (BANK) and program status word (PSWORD) when an interrupt is acknowledged. The saved contents are restored when an interrupt return (RETI) instruction is executed.

INTSK saves data each time an interrupt is acknowledged, but the data stored first is lost if more than 3 levels of interrupts occur.

#### 2.3.3 Stack pointer (SP) and interrupt stack pointer

Table 2-3 shows the operations of the stack pointer (SP).

The stack pointer can take eight values, 0H to 7H. Because there are only five stack registers available, however, the RESET pin is internally pulled down and reset is effected if the value of SP is 6 or greater.

Table 2-3. Operations of Stack Pointer

| Instruction                                              | Value of Stack Pointer (SP) | Counter of Interrupt Stack Register |

|----------------------------------------------------------|-----------------------------|-------------------------------------|

| CALL addr CALL @AR MOVT DBF, @AR (1st instruction cycle) | -1                          | 0                                   |

| PUSH AR<br>SYSCAL entry                                  |                             |                                     |

| When interrupt is acknowledged                           | -1                          | <b>-1</b>                           |

| RET RETSK MOVT DBF, @AR (2nd instruction cycle) POP AR   | +1                          | 0                                   |

| RETI                                                     | +1                          | +1                                  |

#### 2.4 Data Memory (RAM)

The data memory (RAM) stores data for operations and control. It can always be read/written by instructions.

#### 2.4.1 Memory configuration

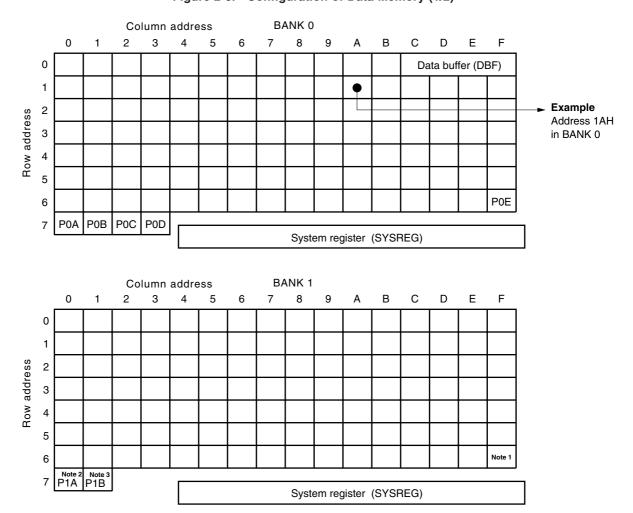

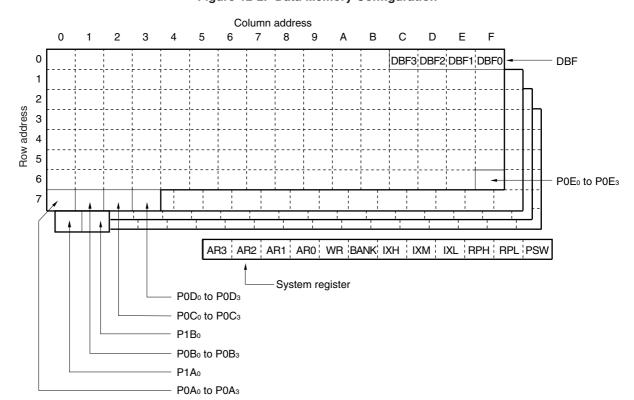

Figure 2-6 shows the configuration of the data memory (RAM).

The data memory consists of four "banks": BANK0, BANK1, BANK2, and BANK3.

In each bank, every 4 bits of data are assigned an address. The higher 3 bits of the address indicate a "row address" and the lower 4 bits of the address indicate a "column address". For example, a data memory location indicated by row address 1H and column address 0AH is termed a data memory location at address 1AH. Each address stores data of 4 bits (= 1 nibble).

In addition, the data memory is divided into the following six functional blocks.

#### (1) System register (SYSREG)

A system register (SYSREG) is resident on addresses 74H to 7FH (12 nibbles) of each bank. In other words, each bank has the same system register at its addresses 74H to 7FH.

#### (2) Data buffer (DBF)

A data buffer is resident on addresses 0CH to 0FH (4 nibbles) of bank 0 of the data memory. The reset value is 0320H.

#### (3) General register (GR)

A general register is resident on any row (16 nibbles) of any bank of the data memory.

The row address of the general register is pointed to by the general register pointer (RP) in the system register (SYSREG).

#### (4) Port register

A port data register is resident on addresses 6FH, and 70H to 73H of BANK0 and addresses 70H and 71H of BANK1 (7 nibbles) of the data memory.

No data can be written to or read from addresses 72H and 73H of BANK1 and addresses 70H to 73H of BANK2 or BANK3.

#### (5) General-purpose data memory

The general-purpose data memory area is an area of the data memory excluding the system register area, and the port register area. This memory area has a total of 447 nibbles (111 nibbles in BANK0 and 336 nibbles (112 nibbles  $\times$  3) in BANK1 to BANK3).

Figure 2-6. Configuration of Data Memory (1/2)

- Notes 1. Address 6FH of BANK1 can be used as a general-purpose data memory area.

- 2. Bits 0 to 2 of address 70H of BANK1 are used. Bit 3 is fixed to 0.

- 3. Only bit 0 of address 71H of BANK1 is used. Bits 1 to 3 are fixed to 0.

Caution No data can be written to or read from addresses 72H and 73H of BANK1.

Column address BANK2 0 2 5 6 8 В D Α 0 Row address 2 3 5 6 System register (SYSREG) BANK3 Column address 0 5 6 В С D 0 Row address 2 5 Note 6

Figure 2-6. Configuration of Data Memory (2/2)

Note Address 6FH of BANK2, BANK3 can be used as a general-purpose data memory area.

Caution No data can be written to or read from addresses 70H to 73H of BANK2 and BANK3.

System register (SYSREG)

# 2.4.2 System registers (SYSREG)

The system registers are registers that are directly related to control of the CPU. These registers are mapped to addresses 74H to 7FH on the data memory and can be referenced regardless of bank specification.

The system registers include the following registers.

- Address registers (AR0 to AR3)

- Window register (WR)

- Bank register (BANK)

- Memory pointer enable flag (MPE)

- Memory pointers (MPH, MPL)

- Index registers (IXH, IXM, IXL)

- · General register pointers (RPH, RPL)

- Program status word (PSWORD)

Figure 2-7. Configuration of System Registers

| Address                         |    | 74 | 4H             |    | 75H 76H     |    |                          |                           |                     |                           |                         | 7                       | 7H                  | ł          | 78H                    |     |   |                |      | 7   | 9H |    |     | 7AH 7BH                                    |             |    |                     |    | 7CH |         |    |     | 7DH |                   |    |    |          | 7         | ΞH | 7F  |    |                  | Н  |             |    |    |    |             |

|---------------------------------|----|----|----------------|----|-------------|----|--------------------------|---------------------------|---------------------|---------------------------|-------------------------|-------------------------|---------------------|------------|------------------------|-----|---|----------------|------|-----|----|----|-----|--------------------------------------------|-------------|----|---------------------|----|-----|---------|----|-----|-----|-------------------|----|----|----------|-----------|----|-----|----|------------------|----|-------------|----|----|----|-------------|

| Name Address register           |    |    |                |    |             |    | Window register          |                           |                     |                           |                         | 3aı                     |                     | or         | Index register<br>(IX) |     |   |                |      |     |    |    |     |                                            |             |    | General<br>register |    |     |         |    |     |     | Program<br>status |    |    |          |           |    |     |    |                  |    |             |    |    |    |             |

| ranio                           |    |    |                |    |             |    |                          | (A                        | (R)                 | )                         |                         |                         |                     |            |                        |     |   | WF             |      | J1  |    | _  |     | Data memory<br>row address<br>pointer (MP) |             |    |                     |    |     |         |    |     |     |                   |    |    | po<br>(R | int<br>P) | er |     |    | word<br>(PSWORD) |    |             |    |    |    |             |

| Symbol                          |    | ΑF | ₹ 3            | }  |             | ΑF | ₹ 2                      | 2                         |                     | ΑI                        | R 1                     |                         |                     | Α          | R                      | 0   |   | ٧              | /R   |     |    | BA | ١N١ | K                                          |             | _  | (H<br>PH            |    |     | IX<br>M |    | IXL |     |                   |    |    | RPH      |           |    | RPL |    |                  |    | PS          |    |    | SW |             |

| Bit                             | Ьз | b2 | b <sub>1</sub> | bo | bз          | b2 | b                        | bo                        | ba                  | b                         | b <sub>1</sub>          | bo                      | b                   | 3 b        | 2 b                    | 1 b | b | b <sub>2</sub> | b    | 1 b | b  | зb | 2b1 | bo                                         | ba          | b2 | b <sub>1</sub>      | bo | ba  | b2      | b1 | bo  | Ьз  | b2                | b1 | bo | bз       | b2        | b1 | bo  | Ьз | b2               | b1 | bo          | bз | b2 | b1 | bo          |

| Data                            | 0  | 0  | 0              | 0  | -( <i>i</i> | AR | <br> <br> <br> <br> <br> | <br> μ<br> <br><b>A</b> R | <br> -<br> <br> ) ( | <br>17<br> <br>μ<br> <br> | <br>24:<br> <br> D1<br> | <br>2,1<br> <br> 72<br> | 72<br> <br> <br> 24 | 24:<br>1)- | 3)-                    | •   |   | (V             | VR   | 1)  | 0  |    | ANI | K)                                         | M<br>P<br>E |    | 0                   | 4  | (   | MF      |    | (IX |     |                   |    | -  | 0        | 0         | -  | (   | RF | 2)               | -  | B<br>C<br>D |    | CY | Z  | I<br>X<br>E |

| Initial<br>value<br>at<br>reset | 0  | 0  | 0              | 0  | 0           | 0  | 0                        | 0                         | 0                   | 0                         | 0                       | 0                       | 0                   | C          | 0                      | 0   | U | nde            | efir | ned | C  | 0  | 0   | 0                                          | 0           | 0  | 0                   | 0  | 0   | 0       | 0  | 0   | 0   | 0                 | 0  | 0  | 0        | 0         | 0  | 0   | 0  | 0                | 0  | 0           | 0  | 0  | 0  | 0           |

#### 2.4.3 General register (GR)

A general register is a register on the data memory and used for arithmetic operations and transfer of data to and from the data memory.

#### (1) Configuration of general register

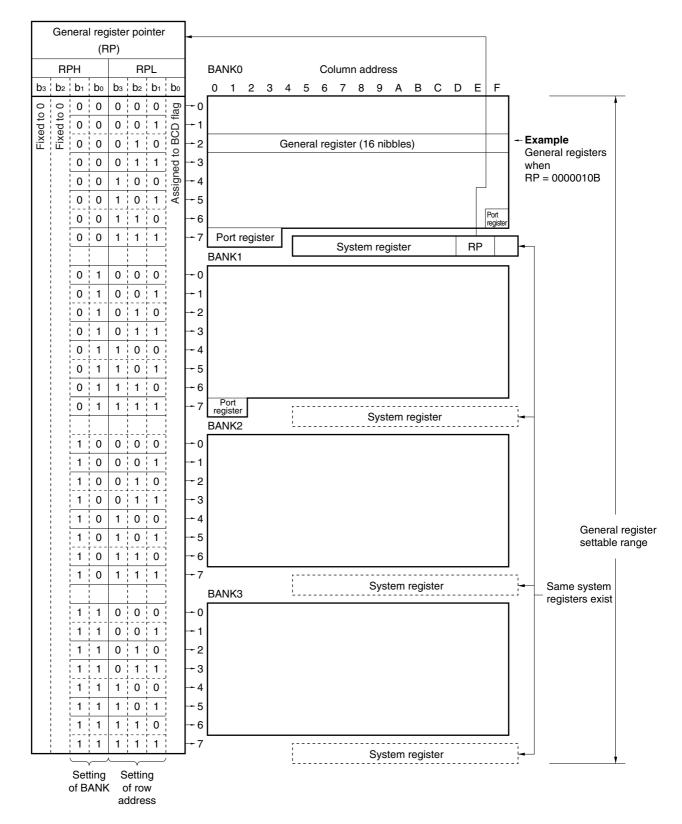

Figure 2-8 shows the configuration of the general registers.

A general register occupies 16 nibbles ( $16 \times 4$  bits) on a selected row address of the data memory as shown in Figure 2-8.

The row address is selected by the general register pointer (RP) of the system register. Five bits of RP are valid. Of these, the lower 3 bits (bits 1 to 3 of RPL) are used to set a row address, and the higher 2 bits (bits 0 and 1 of RPH) are used to set a bank. The data memory that can be used as general registers is at row addresses 0H to 7H in BANK0 to 4.

# (2) Functions of general registers

A general register enables an arithmetic operation and data transfer between the data memory and a selected general register by a single instruction. As a general register is a part of the data memory, you can say that the general registers enable arithmetic operations and data transfer between two locations of the data memory. Similarly, the general registers can be accessed by a data memory manipulation instruction as they are a part of the data memory.

Figure 2-8. Configuration of General Registers

#### 2.4.4 Data buffer (DBF)

The data buffer on addresses 0CH to 0FH of the data memory is used for data transfer to and from peripheral hardware and for storage of data during table referencing.

# (1) Functions of the data buffer

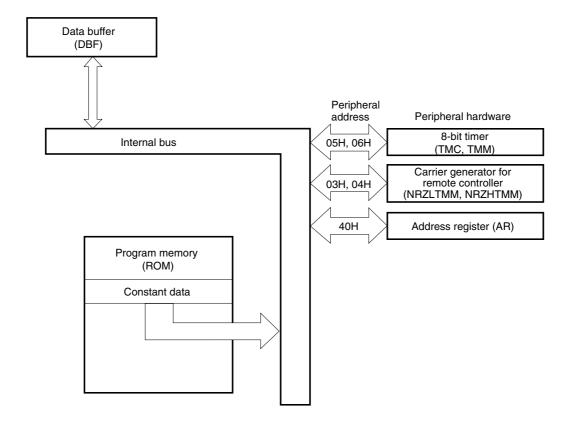

The data buffer has two major functions: a function to transfer data to and from hardware and a function to read constant data from the program memory (for table referencing). Figure 2-9 shows the relationship between the data buffer and peripheral hardware.

Figure 2-9. Data Buffer and Peripheral Hardware

| Peripheral                          | Peripheral Register Transferring Data with Data Buffer |         |                    |                  |                                                |  |  |  |  |  |  |  |  |  |

|-------------------------------------|--------------------------------------------------------|---------|--------------------|------------------|------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Hardware                            | Name                                                   | Symbol  | Peripheral address | Data buffer used | PUT/GET                                        |  |  |  |  |  |  |  |  |  |

| 8-bit timer                         | 8-bit counter                                          | TMC     | 05H                | DBF0, DBF1       | GET only                                       |  |  |  |  |  |  |  |  |  |

|                                     | 8-bit modulo register                                  | ТММ     | 06H                | DBF0, DBF1       | PUT only                                       |  |  |  |  |  |  |  |  |  |

| Remote controller carrier generator | NRZ low-level<br>timer modulo<br>register              | NRZLTMM | 03H                | DBF0, DBF1       | PUT<br>GET                                     |  |  |  |  |  |  |  |  |  |

|                                     | NRZ high-level timer modulo register                   | NRZHTMM | 04H                | DBF0, DBF1       | PUT<br>GET                                     |  |  |  |  |  |  |  |  |  |

| Address register                    | Address register                                       | AR      | 40H                | DBF0 to DBF3     | PUT <sup>Note 1</sup><br>GET <sup>Note 2</sup> |  |  |  |  |  |  |  |  |  |

Table 2-4. Relationship Between Peripheral Hardware and Data Buffer

Notes 1. In the µPD17240: Bits 0 to 3 of AR3 and bit 3 of AR2 are arbitrary values

In the  $\mu$ PD17241: Bits 0 to 3 of AR3 are arbitrary values

In the  $\mu PD17242$ , 17243: Bits 1 to 3 of AR3 are arbitrary values

In the  $\mu$ PD17244, 17245, 17246: Bits 2 to 3 of AR3 are arbitrary values

2. In the  $\mu$ PD17240: Bits 0 to 3 of AR3 and bit 3 of AR2 are always 0

In the  $\mu$ PD17241: Bits 0 to 3 of AR3 are always 0

In the  $\mu$ PD17242, 17243: Bits 1 to 3 of AR3 are always 0

In the  $\mu PD17244$ , 17245, 17246: Bits 2 to 3 of AR3 are always 0

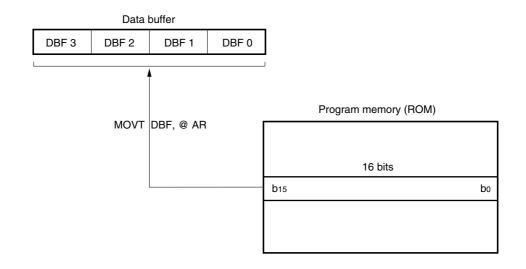

#### (2) Table referencing

An MOVT instruction reads constant data from a specified location of the program memory (ROM) and sets it in the data buffer.

The function of the MOVT instruction is explained below.

MOVT DBF, @AR: Reads data from a program memory location pointed to by the address register (AR) and sets it in the data buffer (DBF).

#### (3) Notes on using data buffer

When transferring data to/from the peripheral hardware via the data buffer, the unused peripheral addresses, write-only peripheral registers (only when executing PUT), and read-only peripheral registers (only when executing GET) must be handled as follows.

#### · When device operates

Nothing changes even if data is written to a read-only register.

If an unused address is read, an undefined value is read. Nothing changes even if data is written to that address.

#### Using assembler

An error occurs if an instruction is executed to read a write-only register.

Again, an error occurs if an instruction is executed to write data to a read-only register.

An error also occurs if an instruction is executed to read or write an unused address.

# • If an in-circuit emulator (IE-17K or IE-17K-ET) is used (when an instruction is executed for patch processing)

An undefined value is read if an attempt is made to read the data of a write-only register, but an error does not occur.

Nothing changes even if data is written to a read-only register, and an error does not occur.

An undefined value is read if an unused address is read; nothing changes even if data is written to this address. An error does not occur.

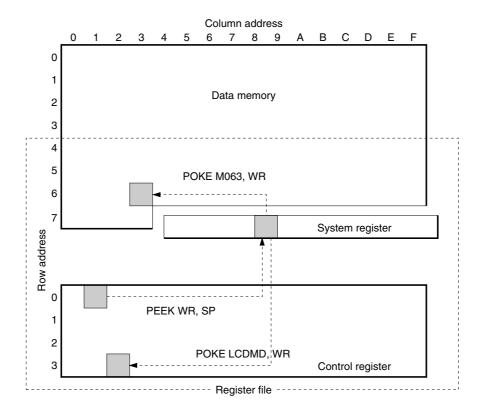

#### 2.5 Register File (RF)

The register file mainly consists of registers that set the conditions of the peripheral hardware.

These registers can be controlled by the dedicated instructions PEEK and POKE, and the embedded macro instructions of RA17K, SETn, CLRn, and INITFLG.

#### 2.5.1 Configuration of register file

Figure 2-10 shows the configuration of the register file and how the register file is accessed by the PEEK and POKE instructions.

The control registers are controlled by using dedicated instructions PEEK and POKE. Since the control registers are assigned to addresses 00H to 3FH regardless of the bank, the addresses 00H to 3FH of the general-purpose data memory cannot be accessed when the PEEK or POKE instruction is used.

The addresses that can be accessed by the PEEK and POKE instructions are addresses 00H to 3FH of the control registers and 40H to 7FH of the general-purpose data memory. The register file consists of these addresses.

The control registers are assigned to addresses 80H to BFH on the IE-17K to facilitate debugging.

Figure 2-10. Register File Configuration and Register File Access with PEEK or POKE Instructions

#### 2.5.2 Control registers

The control registers consist of a total of 64 nibbles ( $64 \times 4$  bits) of addresses 00H to 3FH of the register file.

Of these, however, only 24 nibbles are actually used. The remaining 40 nibbles are unused registers that are prohibited from being read or written.

When the "PEEK WR, rf" instruction is executed, the contents of the register file addressed by "rf" are read to the window register.

When the "POKE rf, WR" instruction is executed, the contents of the window register are written to the register file addressed by "rf".

When using the assembler (RA17K), the macro instructions listed below, which are embedded as flag type symbol manipulation instructions, can be used. The macro instructions allow the contents of the register file to be manipulated in bit units.

For the configuration of the control register, refer to Figure 12-1 Register File List.

SETn: Sets flag to "1" CLRn: Sets flag to "0"

SKTn: Skips if all flags are "1" SKFn: Skips if all flags are "0"

NOTn: Inverts flag

INITFLG: Initializes flag

INITFLGX: Initializes flag

#### 2.5.3 Notes on using register files

When using the register files, bear in mind the points described below. For details, refer to the  $\mu$ PD172xx Subseries User's Manual (U12795E).

#### (1) When manipulating control registers (read-only and unused registers)

When manipulating the write-only (W), the read-only (R), and unused control registers by using an assembler or in-circuit emulator, keep in mind the following points.

#### · When device operates

Nothing changes even if data is written to a read-only register.

If an unused register is read, an undefined value is read; nothing is changed even if data is written to this register.

#### · Using assembler

An error occurs if an instruction is executed to read data from a write-only register.

An error occurs if an instruction is executed to write data to a read-only register.

An error also occurs if an instruction is executed to read or write an unused address.

# When an in-circuit emulator (IE-17K or IE-17K-ET) is used (when an instruction is executed for patch processing)

An undefined value is read if a write-only register is read, and an error does not occur.

Nothing changes even if data is written to a read-only register, and an error does not occur.

An undefined value is read if an unused address is read; nothing changes even if data is written to this address. An error does not occur.

# (2) Symbol definition of register file

An error occurs if a register file address is directly specified as a numeral by the operand "rf" of the "PEEK WR, rf" or "POKE rf, WR" instruction if the 17K Series Assembler (RA17K) is being used.

Therefore, the addresses of the register file must be defined in advance as symbols.

To define the addresses of the control registers as symbols, define them as addresses 80H to BFH of BANKO. The portion of the register file overlapping the data memory (40H to 7FH), however, can be defined as symbols

as is.

#### 3. PORTS

#### 3.1 Port 0A (P0A<sub>0</sub> to P0A<sub>3</sub>)

This is a 4-bit input port. Data is read using port register P0A (address 70H of BANK0). This port is a CMOS input port with a pull-up resistor, and can be used as the key return input lines of a key matrix.

In the standby mode, the standby status is released when a low level is input to at least one of these pins.

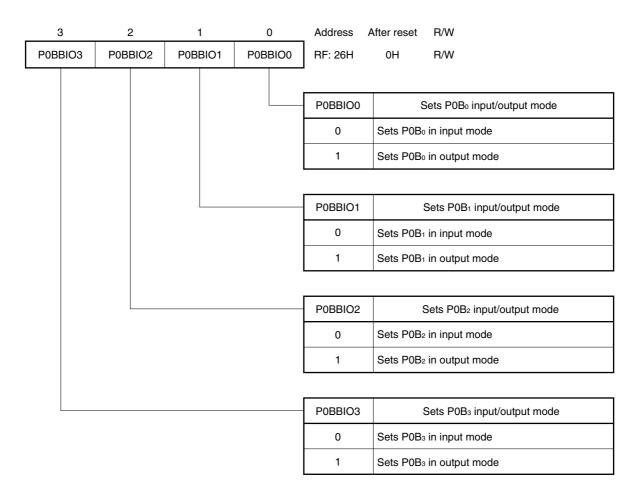

#### 3.2 Port 0B (P0B<sub>0</sub> to P0B<sub>3</sub>)

This is a 4-bit I/O port which can be set to the input or output mode in 1-bit units by using P0BBIO (address 26H) of the register file.

In the input mode, each bit of this port serves as a CMOS input pin with a pull-up resistor and can be used as a key return input line of a key matrix. In the standby mode, the standby status is released when a low level is input to at least one of these pins.

In the output mode, these pins serve as N-ch open-drain output pins and can be used as the key source lines of a key matrix.

The data input to this port can be read or the data output from this port can be set by using the P0B register (address 71H of BANK0). When this port is read in the output mode, the contents of the output latch are read.

In the input mode, a pull-up resistor of 200 k $\Omega$  is connected to each bit of this port. In the output mode, the pull-up resistor is disconnected.

After reset, this port is set to the input mode.

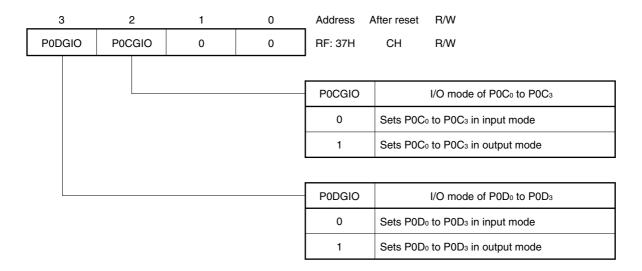

#### 3.3 Port 0C (P0C<sub>0</sub> to P0C<sub>3</sub>)

This is a 4-bit I/O port which can be set to the input or output mode in 4-bit units (group I/O) by using P0CDGIO (bit 2 of address 37H) of the register file.

In the input mode, each bit of this port serves as a CMOS input pin with a pull-up resistor and can be used as a key return input line of a key matrix. In the standby mode, the standby status is released when a low level is input to at least one of these pins.

In the output mode, these pins serve as N-ch open-drain output pins and can be used as the key source lines of a key matrix.

The data input to this port can be read or the data output from this port can be set by using the P0C register (address 72H of BANK0). When this port is read in the output mode, the contents of the output latch are read.

In the input mode, a pull-up resistor of 200  $k\Omega$  is connected to each bit of this port. In the output mode, the pull-up resistor is disconnected.

After reset, this port is set to the output mode and outputs a low level.

#### 3.4 Port 0D (P0D<sub>0</sub> to P0D<sub>3</sub>)

This is a 4-bit I/O port which can be set to the input or output mode in 4-bit units (group I/O) by using P0CDGIO (bit 3 of address 37H) of the register file.

In the input mode, each bit of this port serves as a CMOS input pin with a pull-up resistor and can be used as a key return input line of a key matrix. In the standby mode, the standby status is released when a low level is input to at least one of these pins.

In the output mode, these pins serve as N-ch open-drain output pins and can be used as the key source lines of a key matrix.

The data input to this port can be read or the data output from this port can be set by using the P0D register (address 73H of BANK0). When this port is read in the output mode, the contents of the output latch are read.

In the input mode, a pull-up resistor of 200  $k\Omega$  is connected to each bit of this port. In the output mode, the pull-up resistor is disconnected.

After reset, this port is set to the output mode and outputs a low level.

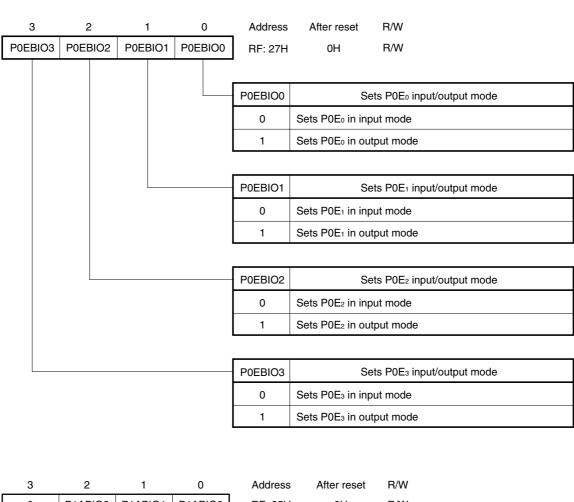

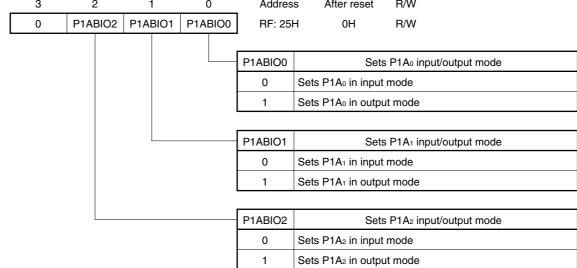

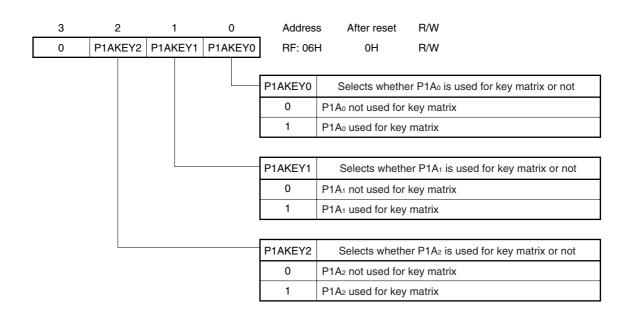

#### 3.5 Port 0E (P0E<sub>0</sub> to P0E<sub>3</sub>)

This is a 4-bit I/O port. The input mode or output mode and whether a key matrix is used or not can be set for this port in 1-bit units.

The input and output modes of this port are selected by using P0EBIO (address 27H) of the register file.

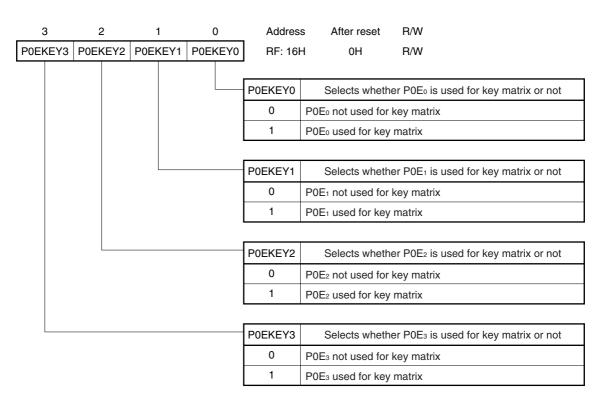

Whether a key matrix is used or not is specified by P0EKEY (address 16H) of the register file.

If this port is set to the input mode when a key matrix is used, it functions as a CMOS input port with a pull-up resistor and can be used to input key return signals. If one of the pins of this port goes low, the standby mode is released.

If this port is set to the output mode when a key matrix is used, it functions as an N-ch open-drain output port and can be used to output key matrix signals.

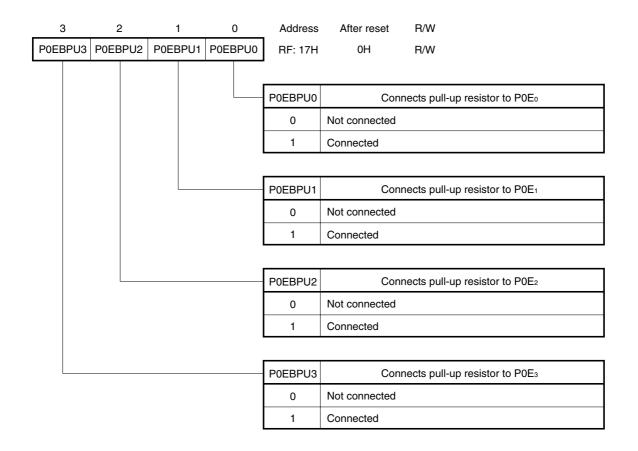

If this port is set to the input mode when a key matrix is not used, it functions as a CMOS input port to/from which a pull-up resistor can be connected/disconnected in 1-bit units, by using P0EBPU (address 17H) of the register file (if a pull-up resistor is connected, it is not disconnected even if the output mode is set). At this time, the standby mode is not released.

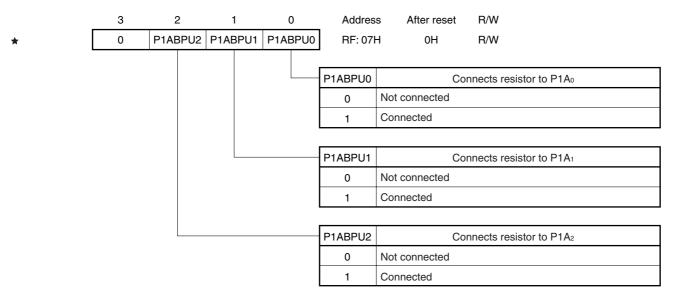

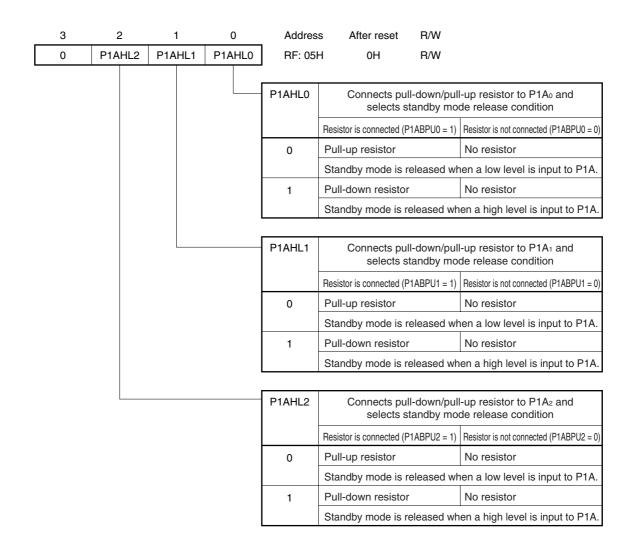

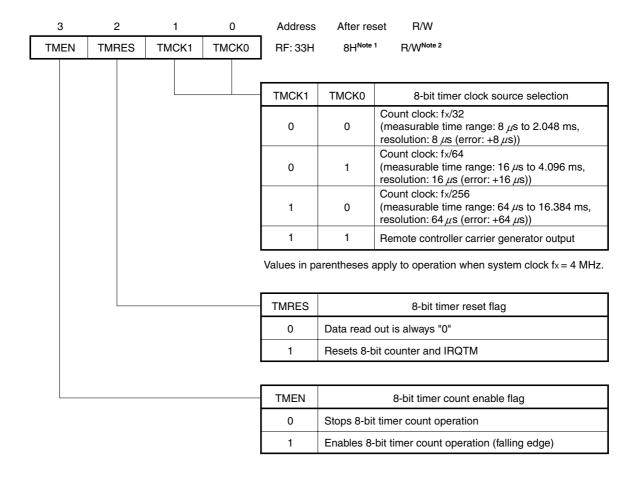

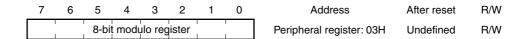

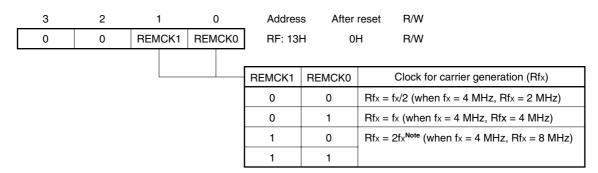

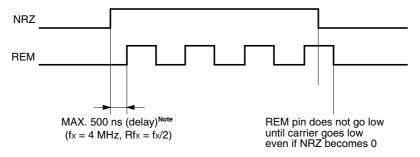

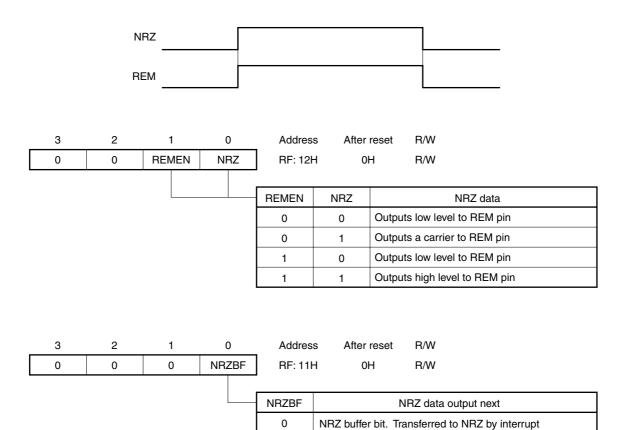

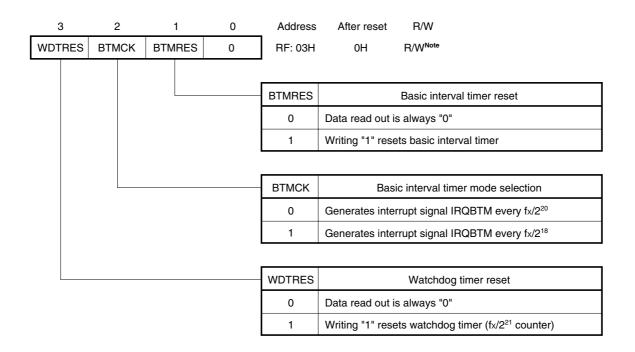

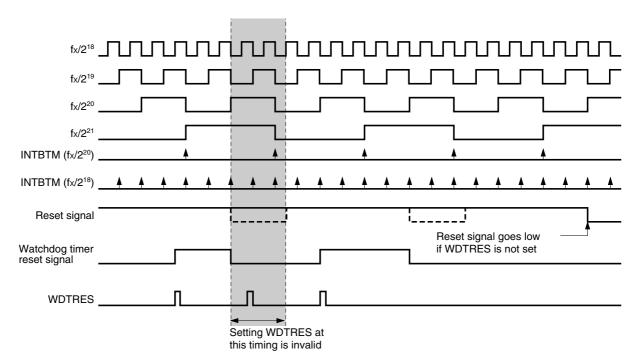

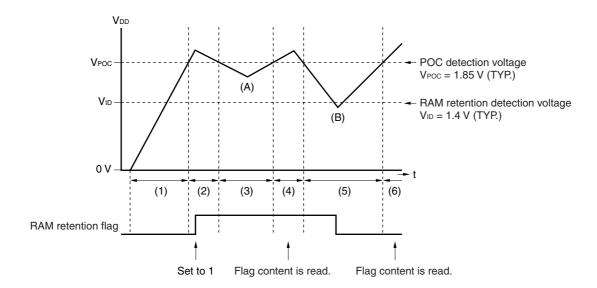

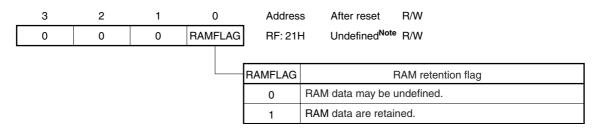

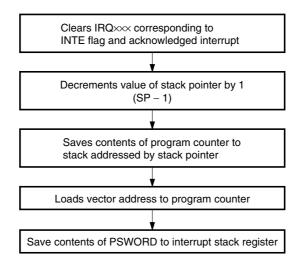

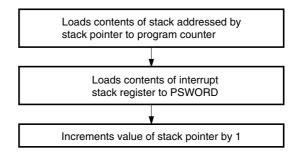

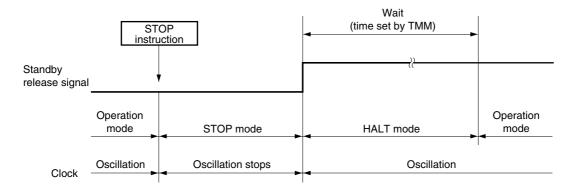

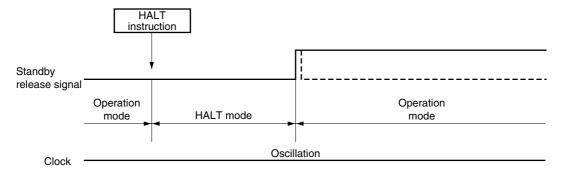

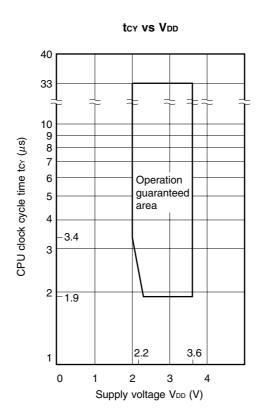

If this port is set to the output mode when a key matrix is not used, it functions as a high-current CMOS output port. To read the input data from this port or set output data to it, use the P0E register (address 6FH of BANK0). When this port is read in the output mode, the contents of the output latch are read.